Reducing the Battery Cost of Battlefield Situational Awareness

The massive growth in the number of sensing devices worn by soldiers and placed in the battlefield creates new opportunities, such as soldier biosensing and better situational awareness. But these sensors must all acquire and communicate data over long periods of time, which creates new challenges for system designers— from larger batteries that soldiers must carry in order to power all of these sensors, to a glut of sensor data that overloads network bandwidth and analyst resources.

This trend to collect more and more data puts a strain on the digital system that collect and analyze the sensor information. Nevertheless, designers of battlefield sensing systems invariably

gravitate to these digital processing architectures, including microcontrollers and digital signal processors, because the last three decades have seen significant digital processing improvements,

and because small and programmable analog architectures have not been available until now.

Recent innovations in analog signal processing [1] make it possible to analyze or screen the data in the sensor’s analog domain so only the desired information passes to the rest of the signal chain—a technique that affords a 10x overall power reduction in many sensor systems (including acoustic, vibration and bio-sensing applications), while also reducing the size and cost of these systems.

Data Reduction and Analytics at the Sensor “Edge”

Power consumption is a key challenge facing battlefield-deployed sensor systems, and the other big challenge is to deal with the large amount of data generated by innumerous sensor nodes in the battlefield or on the soldiers. To reduce network bandwidth requirements, some of these analytics are pushed from the cloud to the “edge” of the network on the sensor nodes; however, the ability to perform these analytics at the sensor edge is limited by the cost of supplying sufficient battery power into the battlefield.

Today, edge devices are typically “dumb” by necessity, because designers cannot afford to compromise the battery life of the device with significant processing. Consequently, these edge devices generate a deluge of irrelevant data that are not filtered until reaching the gateway or the cloud. With low-power analog processing, the system can afford the power cost to reduce the sensor data to only the data that are desired for the application.

Early identification of key data will provide cost and efficiency advantages at all layers of the signal chain by enabling each layer to only process and send the relevant data, and will provide performance advantages in back-end data analytics by allowing developers to redirect their focus away from finding relevant data and on to building upon relevant data.

Analog Signal Processing—Efficient, Programmable and Small

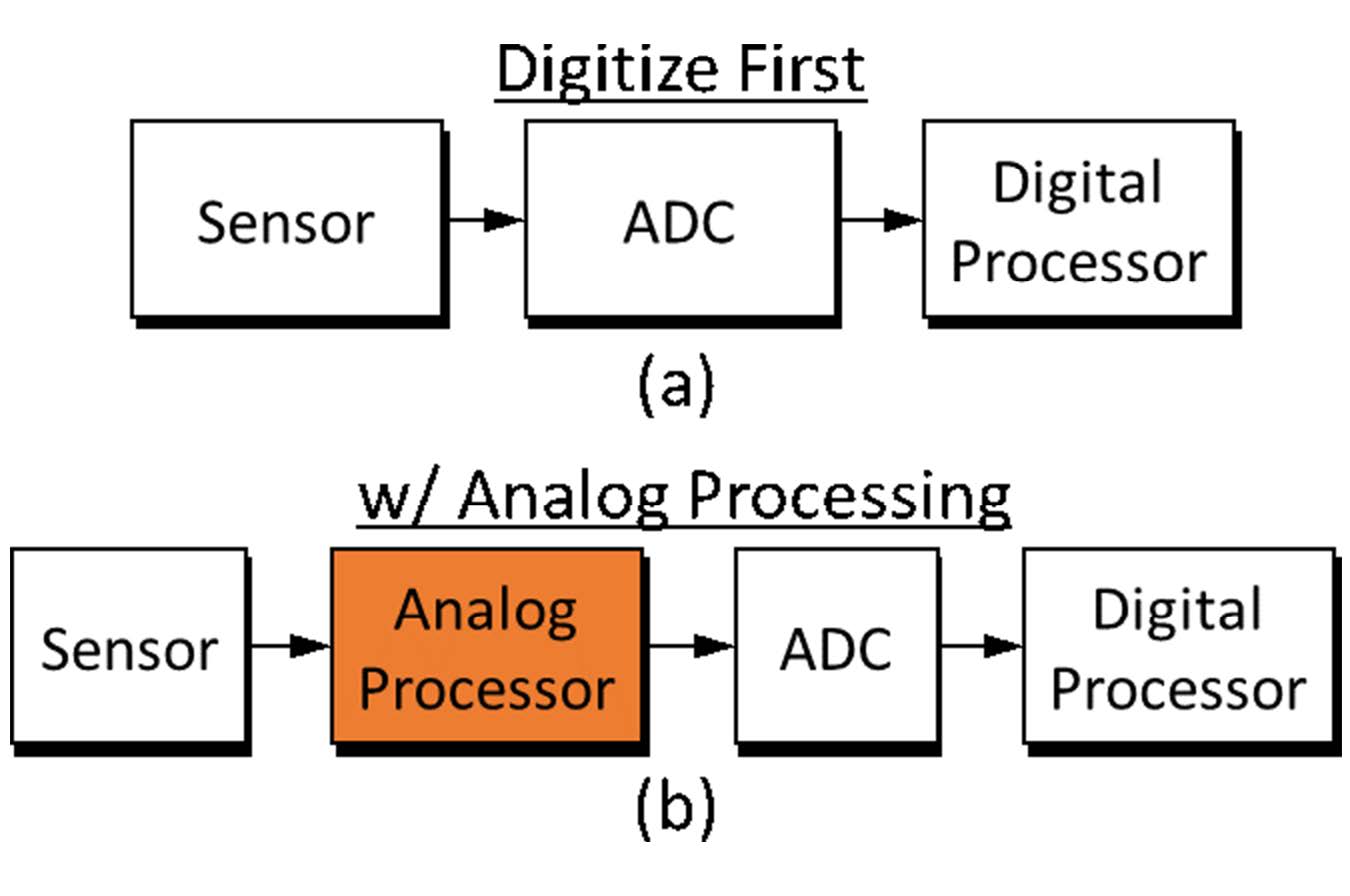

Efficiencies in both power and data reduction can be understood by exploring embedded sensor architectures and understanding how analog processing can provide significant benefits. In the traditional embedded sensor architecture shown in Figure 1(a), data processing starts with digitizing — via the analog-to-digital converter — all of the analog data from the sensor. This raw digital data may then be transmitted for offline analysis, but it is generally desirable to minimize transmission by first reducing the raw data to relevant information using the digital processor, and then act on this information by, for example, notifying the soldier or transmitting the data upstream for further action.

This process can be extremely inefficient, since all of the data, whether valuable or not, are first digitized by the ADC — which often dominates the power consumption of optimized systems — and then processed by the digital processor — which may alternatively dominate the power consumption. This inefficiency is quite dramatic in higher- bandwidth sensor systems. For example, in acoustic systems, the ADC power is significant due to the speed and resolution requirements, and it is also important to analyze all of the sensor data, even though most of the data are not critical for the application.

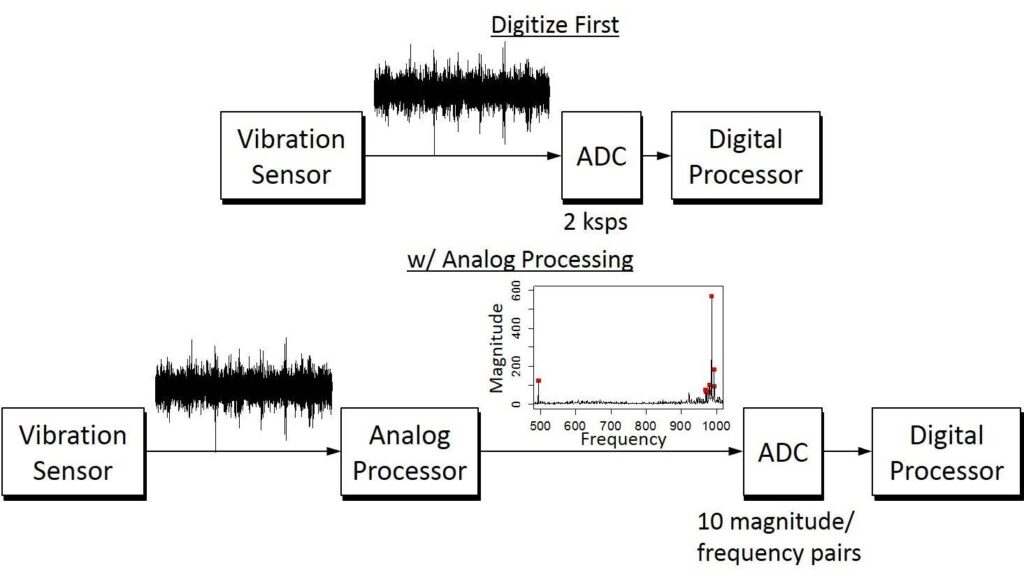

Figure 1: Sensor processing architectures. (a) Traditional approach where all processing is digital. (b) New paradigm where an analog processor “screens” the data so that system resources are not wasted on irrelevant data. (Released)

To improve efficiency, an analog signal processor may be inserted between the sensor and ADC, as shown in Figure 1(b). By programming the ASP with sophisticated signal processing and detection algorithms, tasks that are typically digital can be performed earlier in the sensor signal chain (prior to digitization), thereby reducing the system’s throughput requirements and power

consumption; consequently, the size and cost of the signal chain componentry and battery are also reduced. To reap these benefits, this paradigm requires low-power, programmable analog processors, which are enabled by recent innovations in low-power analog processing circuits, [2] nonvolatile analog memory [3] and programmable analog architectures. [1] The efficient signal-chain architecture shown in Figure 1 (b) can be achieved with the addition of an analog processor integrated circuit. [1] This innovative architecture provides significant benefits to sensor systems

in the battlefield. These benefits are discussed further below, as well as applicability of the technology in acoustic, bio-sensing, and vibration systems.

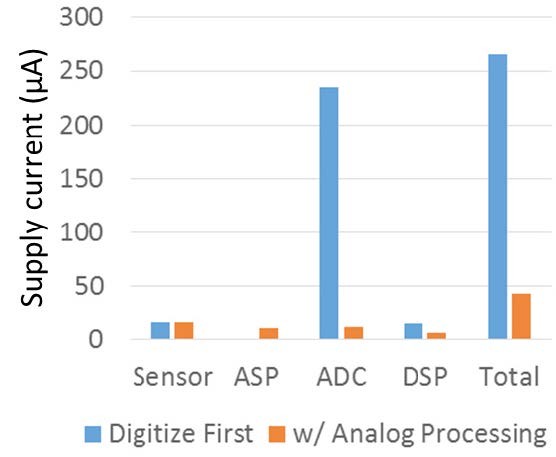

As discussed above, the power consumption of battlefield systems with higher-bandwidth sensors is typically dominated by the ADC and the digital processor. The most effective way to address this power consumption is to reduce the activity of the ADC and digital processor. This is accomplished today by either duty cycling those components — which risks the loss of important data — or by adding an “always- on” low-power DSP that wakes up the digital processor based upon the signal content — which still incurs the power consumption of an always-on ADC. Since ADC

power consumption does not scale nearly as aggressively with the technology node as does the power consumption of digital logic, [4] the ADC will dominate even more of the system’s power consumption in the future. The alternative approach in this article is to reduce the quantity of data that are digitized by performing data analysis in the analog domain. Fewer data are digitized,

thereby better balancing the power budget across the signal chain. Figure 2 compares the always-on power breakdown of the two approaches in an acoustic “wake-on-voice” application. By frontloading some of the DSP tasks into the ASP, the ADC power — and thereby the system power — has been significantly reduced.

Figure 2: Power breakdown of the architectures shown in Figure 1 for a “wake-on-voice” application. (Released)

Analog processing has been shown to be more efficient than digital processing in low-to-moderate precision applications, [5] such as embedded sensors and perceptual processing algorithms (e.g. acoustic processing, where the instantaneous dynamic range of speech is only 30-35dB [6]). In these types of applications, complex signal processing algorithms use nonlinear operations for scale-invariant feature extraction [7] and to represent statistical models. [8] Analog circuits can provide small and efficient realizations of these nonlinear operations, because the nonlinear operations can be built from the large-signal characteristics of a small number of circuit elements, [9] whereas digital implementations require inefficient lookup tables or iterative methods to realize the same operations. As a result, analog processing can provide efficient analytics at the edge, which benefits battlefield operations by significantly reducing the power supply demands.

While analog processing is not a new paradigm, one of its key challenges has been to field small form factor analog processing architectures. With recent innovations in programmable, non-linear analog architectures, sensor system designers now have the ability to build programmable analog processing blocks with a much smaller programming overhead as compared to currently available analog and digital architectures. This enables an IC implementation of current application architectures in a much smaller footprint that, in some scenarios, can efficiently fit inside the sensor transducer. This small size is achieved in mature, and less expensive, CMOS process technologies. Additionally, since the ASP’s data reduction reduces the processing and memory requirements of the system, it is possible to significantly reduce or totally eliminate some of the downstream blocks and ICs, thereby reducing total system size and cost further. In the end, analog signal processing may enable small, disposable sensors for use in the battlefield.

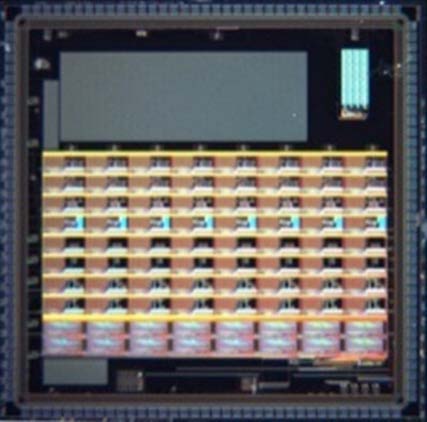

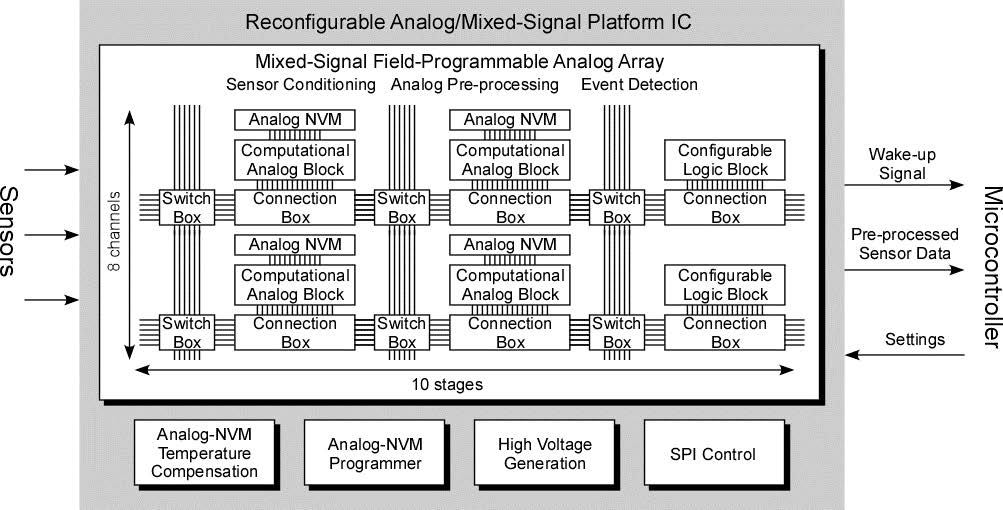

Analog algorithm development has been accelerated by the Reconfigurable Analog/ Mixed-Signal Processor architecture, which received the best paper award at the International Symposium on Quality Electronics Design. [1] This architecture (See Figure 3) combines a large-scale programmable analog processor IC with analog application software. The architecture is fully programmable,

and even allows reprogramming in a deployed environment, such as on the battlefield. The 5mm x 5mm architecture is an array of blocks, so it is also scalable for small form-factor applications — e.g., an acoustic event detection architecture may be as small as 0.5mm x 0.5mm. The RAMP architecture (See Figure 4) is a field-programmable analog array — similar to a digital FPGA — and consists of an array of circuits that can be reconfigured via a switch fabric. In contrast to other FPAAs (e.g. [10] and [11]), the RAMP has been designed for sensor processing: it is arranged in a stage based processing flow that proceeds from sensor interfacing, to feature extraction, to pattern recognition, to mixed-signal and digital circuits — and it is self-contained and can be reprogrammed over a simple serial interface. It provides analog re-programmability with a focus on low-power analog signal processing. For example, the Computational Analog Blocks include circuits for feature extraction and pattern recognition. A development environment helps with high-level creation of more complex algorithms.

Military Applications

Analog processing is quite beneficial to high-bandwidth sensor applications for the battlefield where it is important to analyze all of the data. In these high-bandwidth systems, it is much more efficient to use analog processing to analyze the data prior to the digitization phase, and thereby avoid digitizing all of the data and wasting power. With a power reduction of up to 10x in sensing and communications circuitry, the total power requirement of the system can be greatly reduced. This reduction in power enables the use of smaller, lighter batteries, and possibly enables operational use of energy-harvesting technologies (e.g. solar) which are not adequate to power today’s sensing and communications systems. The RAMP ASP technology can be configured/programmed for a number of different sensor paradigms and application tasks, all at much lower power levels than seen in today’s implementations.

Figure 3: Reconfigurable Analog/Mixed-Signal Processor IC.(Released)

Acoustics

Acoustic, or audio, applications can benefit greatly from ASP technology. Analog processing can extract audio features — e.g. voice, short-term SNR in a frequency band, or long-term audio features like background noise statistics — to aid later digital processing. To do this, it is important that all of the sensed data are analyzed so that critical data are not overlooked. This staged approach saves power by keeping later stages in sleep mode until needed. The RAMP architecture enables the ability to perform audio signal processing in the analog domain, thereby analyzing the audio and determining “voice” or “non-voice” triggers at a power level about 10x lower than current solutions. This power reduction is realized by leveraging low-power analog circuitry and by keeping the ADC and DSP circuity in sleep mode until a trigger is detected. Additionally, the ASP can offload DSP tasks such as noise suppression and gain normalization to obtain additional power savings.

Voice activity detection is a good example of system power reduction using analog processing. In voice-control systems, the first step is to determine whether a voice is heard. Since upwards of 90 percent of the audio that is detected by the microphone is not voice, the “digitize first” approach wastes significant power by digitizing and processing all of the audio (duty cycling is not an option) in search of voice to trigger the next stage of voice control. In contrast, the VAD algorithm can be placed in an analog processor, which generates a “wake-onvoice” signal to trigger the ADC and DSP to wake up and analyze the voice for keyword or voice-command processing. This approach provides a 10x reduction in power as compared to today’s leading competitive solutions—from 300μA supply current for a complete microphone/ADC/digital VAD solution to 30μA for a microphone/analog VAD solution. Figure 2 shows this power breakdown. Voice triggering could be a key complement to the battlefield soldier, and allow mechanical systems to remain off until voice is detected or a specific keyword is triggered.

In addition to voice, the RAMP solution can be programmed for acoustic surveillance systems to analyze acoustic sensor data for non-voice signatures as well. This could include key battlefield surveillance items such as classification and identification capabilities for continuous sources (vehicles, aircraft, etc.) and impulsive sources (gun fire, artillery impacts, etc.). An early ASP demonstrated an analog algorithm for acoustic vehicle surveillance [12] that can be used at remote battlefield outposts. The algorithm detects vehicle activity and classifies the type of vehicle. That prototype system was demonstrated to have 90% accuracy at a power consumption that will increase the monitoring system lifetime from 4 months (for current digital implementations) to 9 years on a pair of AA batteries.

Bio-Sensing

Soldier health and status are key indicators in demand on the battlefield, and the RAMP architecture can provide insight into these parameters, albeit at a much lower power cost than other solutions. With the architecture, one can monitor the average heart rate and other metrics as is typically done with current digital-based solutions; however, it would be much more efficient to focus on the “out of normal” measurements. For instance, the RAMP could be programmed to look for a particular heart rate or a heart arrhythmia, indicative of a specific situational analysis. Once detected, a “trigger” could be sent and a specific measure could be taken. The RAMP has been used to demonstrate an out-of-range heart-rate system that draws just 7μA of supply current [1]. The key to this scenario is remaining “always-on” and looking for the “out of normal” signature at very low power, which is best accomplished with an analog processor solution.

Figure 4: Architecture of RAMP analog signal processor IC. A mixed-signal field-programmable analog array provides efficient signal-processing

capabilities. (Released)

Vibration Monitoring

Vibration monitoring provides a good example of how analog processing at the edge sensor device can significantly reduce data. In mechanical systems or equipment deployed on the battlefield, machinery wear or maintenance downtime (which occurs regularly but is unpredictable) has detrimental impacts. In these systems, monitoring the vibration characteristics offers a glimpse

into early troubles and allows preventative maintenance. One challenge in vibration monitoring is how to handle the large quantities of vibration data that are generated by the vibration sensors that are distributed throughout a mechanical structure or machine. Vibration data are captured at a moderately high frequency (up to tens of kilohertz), and thus generate a significant amount of data for an embedded sensing device. This abundance of data requires more powerful processors and greater power consumption.

Vibration monitoring devices digitize all of the data and then perform an FFT on the data. Peaks in the FFT spectra indicate the vibrational modes of the monitored structure, and the health of the structure can then be inferred from the relationship between the vibrational modes. Essentially, the desired vibration information is contained within a relatively small number of data points (i.e.

the modes), so by extracting this information earlier in the signal chain—prior to digitizing the signal—the necessary resources for an embedded vibration monitoring device can be significantly reduced. Extracting these modes with analog processing provides a 100x reduction in the data that must be digitized and handled by the processor — from 2048 data points for an FFT frame to

10 pairs of frequency and magnitude datum. This process is illustrated in Figure 5. While data reduction is a key benefit to vibration monitoring applications, analog processing will provide additional benefits to the power, size, and cost of the entire solution.

In addition to the continuous reduction of vibration data described above, analog processing can also provide vibration event detection similar to acoustic event detection like voice or vehicle detection. In battlefield surveillance systems employing seismic (vibrational) measurements, vehicles and footsteps are recognized by their seismic signatures. An ASP can be programmed to

trigger on these signatures, which significantly reduces the power requirements of unattended ground sensors.

Figure 5: Application of analog pre-processing to vibration monitoring. The analog processor extracts the vibration modes and thus reduces the data that must be digitized by 100x. (Released)

Conclusion

The military and Department of Defense agencies have a significant need to improve energy efficiency in the field, especially with the massive growth of sensors and of data capture / analysis. While digital processing has been used in most settings because it is flexible, easy to program, robust to noise, and also benefits from technology scaling, analog processing is able to operate in real-time and perform many computations inherently that require significant overhead and power consumption in the digital domain. Additionally, the requirement to digitize the ever growing amount of analog-based sensor data makes digital processing an even less efficient option. The alternative to digital processing is programmable analog circuity, which has been in existence for many years, but recent innovations make it more efficient, flexible, and easy to use, which will accelerate the development of sensor systems using analog processing. Essentially, any application requiring low-power sensors and higher data bandwidths will benefit from an ASP solution for reduced system power consumption and reduced data requirements, which in turn has the potential to reduce the cost of the system and simplify the design of the end product.

References

1. Rumberg, B. and Graham, D. (2015). A low-power field-programmable analog array for wireless sensing. International Symposium on Quality Electronic Design.

2. Ravindran, S., Smith, P., Graham, D., Duangudom, V., Anderson, D., and Hasler, P. (2005). Towards low-power on-chip auditory processing. EURASIP Journal on Applied Signal Processing. 7, 1082-1092.

3. Rumberg, B. and Graham, D. (2012). A floating-gate memory cell for continuous-time programming. IEEE Midwest Symposium on Circuits and Systems.

4. Hasler, P. and Anderson, D. (2002). Cooperative analog-digital signal processing. IEEE International Conference on Acoustics, Speech, and Signal Processing.

5. Sarpeshkar, R. (1998). Analog versus digital: Extrapolating from electronics to neurobiology. Neural Computation. 10, 1601-1608.

6. Chasin, M. (2007, Feb. 12). Music as an Input to a Hearing AId. Retrieved from www.audiologyonline.com/articles/music-as-input-to-hearing-954 (accessed October 30, 2016).

7. Schwartz, O. and Simoncelli, E. (2001). Natural signal statistics and sensory gain control. Nature Neuroscience. 7, 819-825.

8. Duda, R., Hart, P., and Stork, D. (2000). Pattern Classification. Wiley.

9. Mead, C. (1989). Analog VLSI and Neural Systems. Addison-Wesley.

10. Anderson, D. et al. (1997). A field programmable analog array and its applications. Proceedings of the IEEE Custom Integrated Circuits Conference.

11. Basu, A., Brink, S., Schlottmann, C., Ramakrishnan, S., Petre, C., Koziol, S., … and Hasler, P. (2010). A floating-gate-based field-programmable analog array. IEEE Journal of Solid-State Circuits. 45(9), 902-922.

12. Rumberg, B., Graham, D., Kulathumani, V., and Fernandez, R. (2011). Hibernets: Energy-efficient sensor networks using analog signal processing. IEEE Journal on Emerging and Selected Topics in Circuits and Systems.1(3), 321-334.

13. Rumberg, B. and Graham, D. U.S. Patent 9,218,883 B2. Continuous-time floating gate memory cell programming.

14. Rumberg, B. and Graham, D. (2013, March). U.S. Patent 9,218,883 (Issued). Continuous-time floating-gage memory cell.